cst如何使用partial rlc提取宽带spice-博天堂登陆

作者 | wang yuanteng

通常,单一频点导出的spice网表是可读的,并且只描述结构在该频率下的行为。对于不需要可读性但希望在整个频段上进行精确建模的情况,我们希望使用宽带spice。

虽然仿真实例013:ic封装的rlc提取以及等效电路中曾经提到过,“rlcg生成的spice都是单独频点的结果,想要得到宽带的spice需要用s参数加idem工具进行转换”。但时过境迁,尽管关于partial rlc的内容更新较少,其实partial rlc早就可以提取宽带spice了。

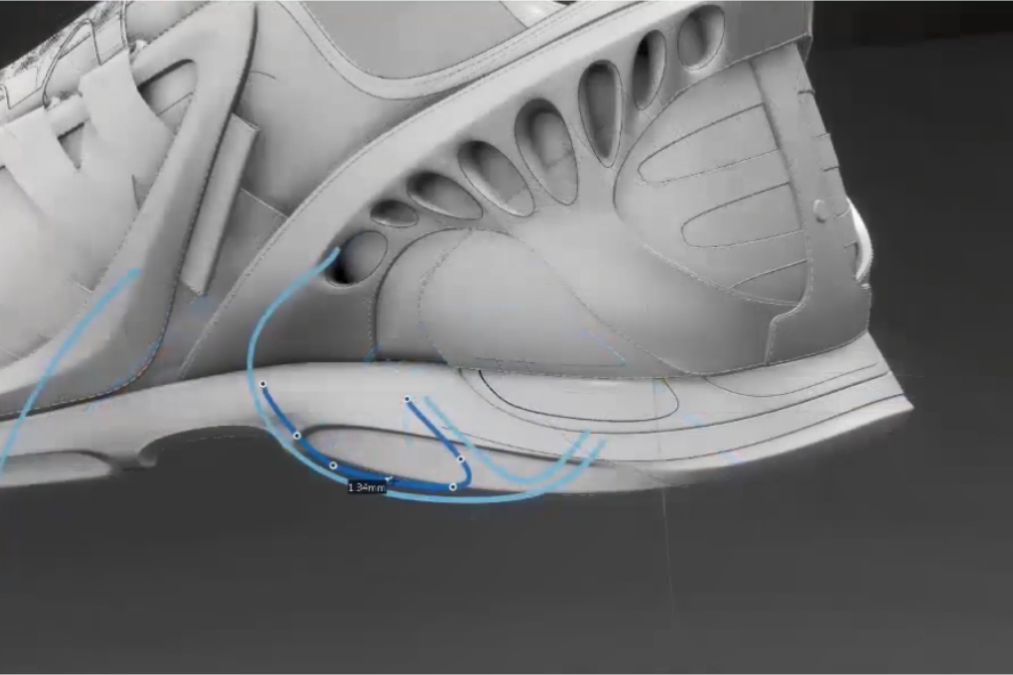

我们以component library中的bondwire为例,来看一下具体提取方法。

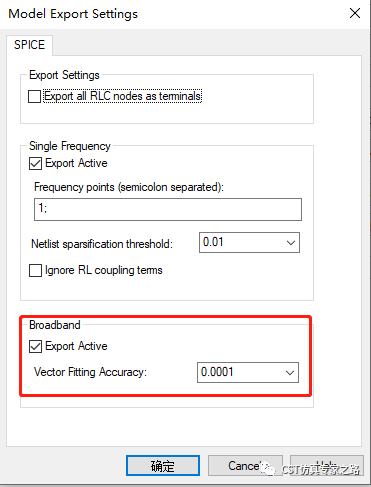

打开bondwire工程,在求解器设置界面,选择export settings。

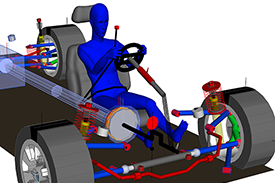

弹出设置界面:

中间是原有的单频点导出功能,可以设定若干个频点。下方即导出宽带spice功能。该功能中,求解器使用矢量拟合算法生成spice,故同时可设置拟合精度。

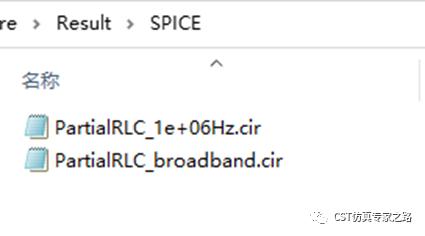

设置完成之后,点击求解器start,仿真结束后即可在工程文件夹下,result>spice下找到spice文件。

另外,值得一提的是,相比之前仿真实例010:提取局部电感电阻(2020版新功能)和仿真实例013:ic封装的rlc提取以及等效电路中介绍的一些功能细节,目前partial rlc求解器有一些显著的更新。例如,可以支持open 边界,增加了网格自适应功能、电流可视化等功能。感兴趣的小伙伴可以自己在新版本体验,帮助文档中亦有相关功能说明。

(内容、图片来源:cst仿真专家之路公众号,侵删)

博天堂登陆的版权与免责声明:

凡未注明作者、来源的内容均为转载稿,如出现博天堂登陆的版权问题,请及时联系918博天堂官网处理。我们对页面中展示内容的真实性、准确性和合法性均不承担任何法律责任。如内容信息对您产生影响,请及时联系918博天堂官网修改或删除。

-

2023-12-29

-

2023-12-29

-

2023-12-29

-

2023-12-28

-

2023-12-28

-

2023-12-28

-

2023-12-27

-

2023-12-27

-

2023-12-27

-

2023-12-26

-

[abaqus] abaqus如何建模?abaqus有限元......

2023-07-07

-

2023-08-24

-

[abaqus] 关于2013版的thinkdesign用......

2014-06-20

-

2017-05-19

-

[abaqus] thinkdesign技术在创新设计中的......

2015-03-03

-

[abaqus] 基于thinkdesign回弹补偿功能的......

2015-03-03

-

[abaqus] td styling之眼镜三维建模、渲染......

2015-03-03

-

2015-03-03

-

2023-08-29

-

2015-03-03

-

[有限元知识] abaqus分析指南120:裂纹萌生与扩......

2023-12-29

-

[有限元知识] abaqus分析指南119:将内聚材料概......

2023-12-29

-

2023-12-29

-

2023-12-28

-

[有限元知识] abaqus分析指南116:多个丰富的功......

2023-12-28

-

[有限元知识] abaqus分析指南115:用水平集方法......

2023-12-27

-

[有限元知识] abaqus分析指南114:水力驱动裂缝......

2023-12-27

-

[有限元知识] abaqus分析指南113:基于内聚段法......

2023-12-26

-

[有限元知识] abaqus分析指南112:有限元方法将......

2023-12-26

-

[有限元知识] abaqus分析指南111:温度和场变量......

2023-12-26

地址: 广州市天河区天河北路663号广东省机械研究所8栋9层 电话:020-38921052 传真:020-38921345 邮箱:thinks@think-s.com

博天堂登陆 copyright © 2010-2023 广州思茂信息科技有限公司 all rights reserved. 粤icp备11003060号-2