cst如何在chip interface中设置沉积共形?-博天堂登陆

作者 | wang yuanteng

我们在faq131:如何使用chip interface导入gdsii文件?中介绍过使用process queue模拟ic制造的步骤。其中沉积是其中非常重要的步骤,那么如何设置沉积共形呢?

下面我们以一个具体模型为例,介绍沉积共形的设置方法。

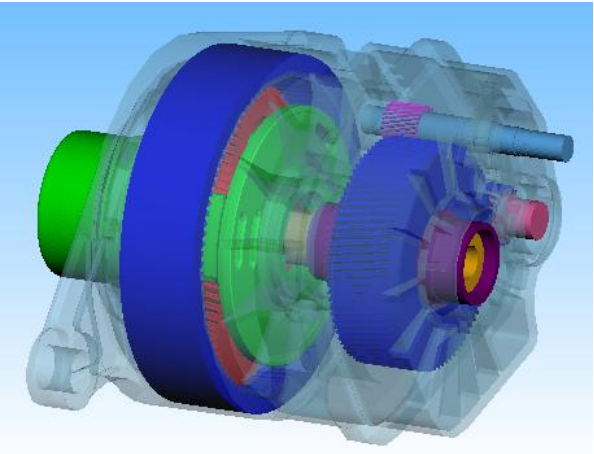

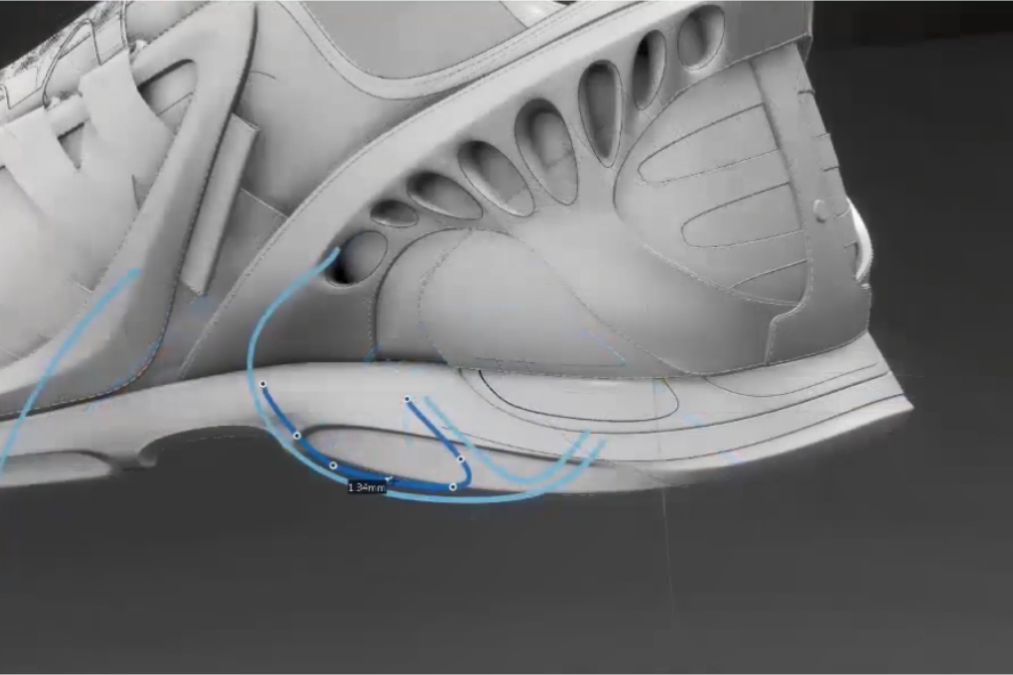

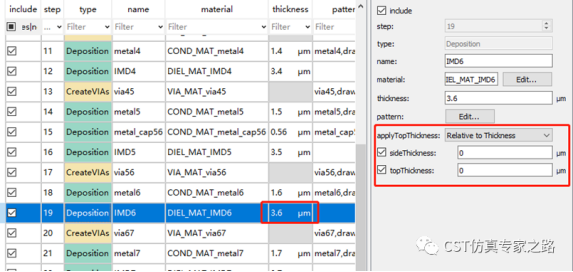

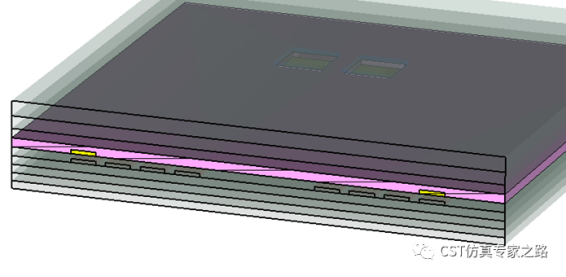

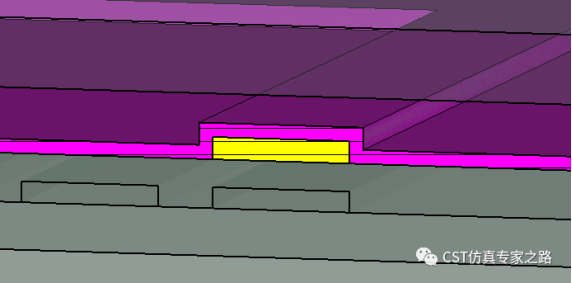

该例中,图中所示粉色部分为沉积层imd6,厚度为3.6um,图中黄色部分为上一步生成的金属层metal6。此时,沉积层设置为默认设置,从图中可以看出并无共形。

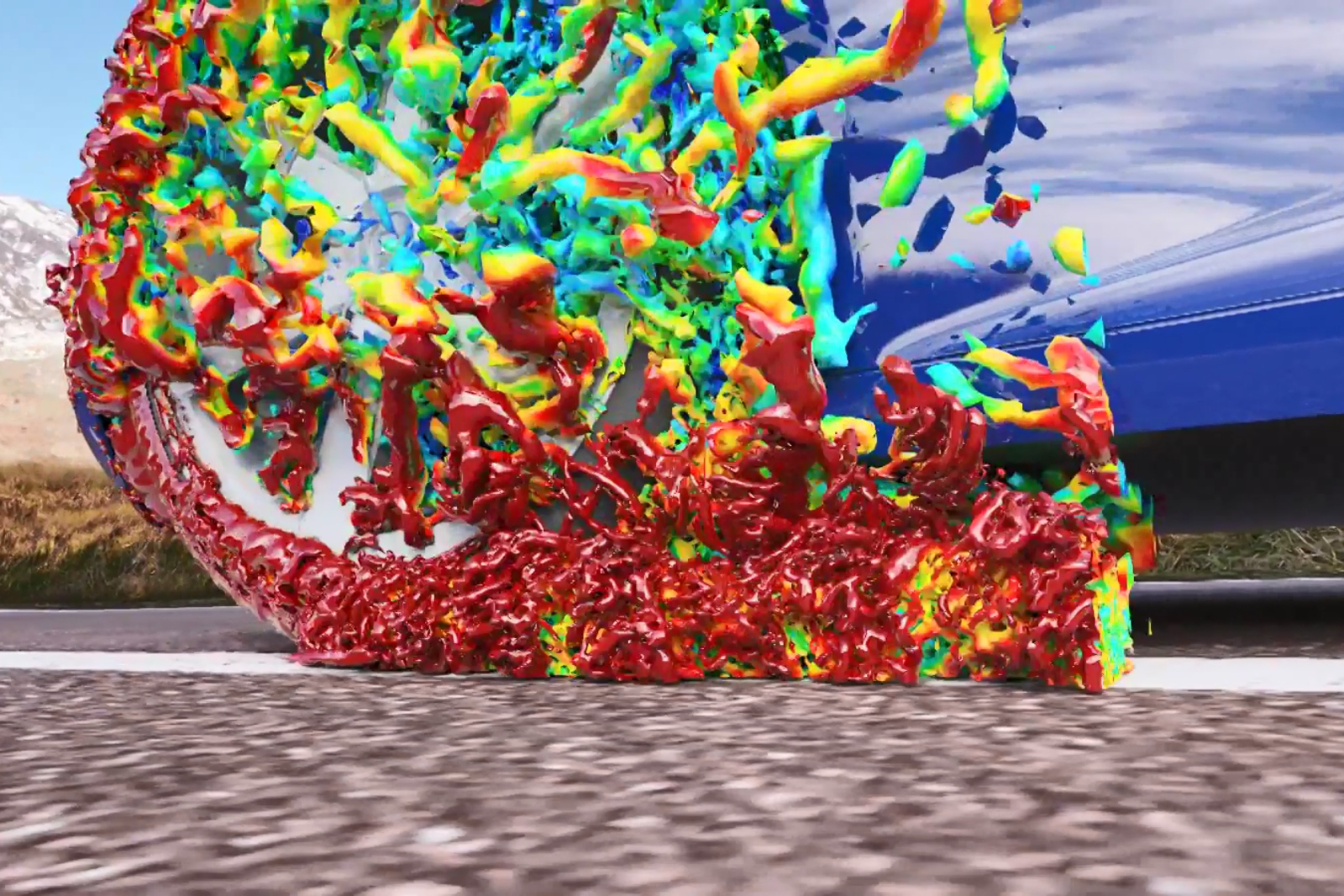

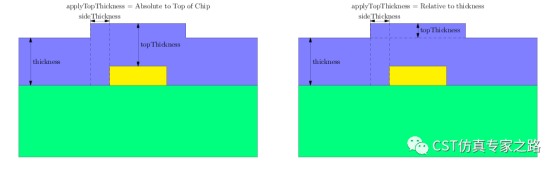

参考帮助文档,其中对沉积共形设置做了明确解释:

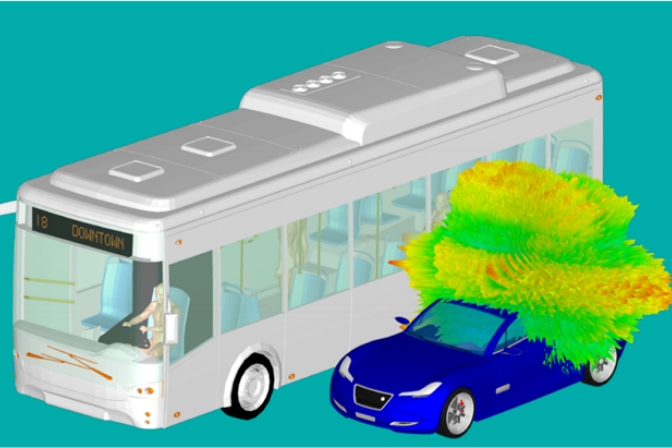

沉积共形由3个厚度决定,分别是图中的thickness、sidethickness和topthickness。其中,topthickness的定义方式有两种,可以是参考到芯片上方的absolute to top of chip,也可以是参考到整个沉积层的relative to thickness。另外,如果未指定sidethickness,那么该值与thickness相同。同样的,如果topthickness没有指定的话,也被认为等于thickness。

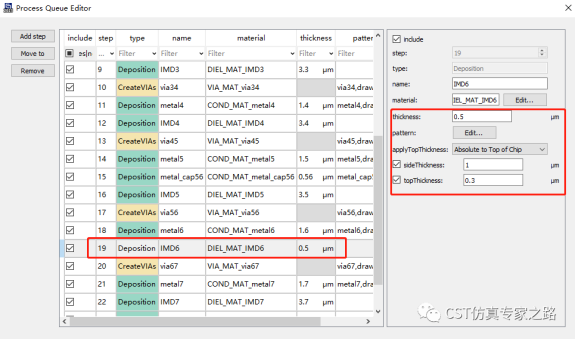

了解清楚后,我们尝试一下修改沉积共形设置如下。将沉积层整体厚度改为0.5um,sidethickness为1um,topthickness为absolute to top of chip 0.3um,也就是芯片上面高出0.3um。

生成沉积共形效果如下:

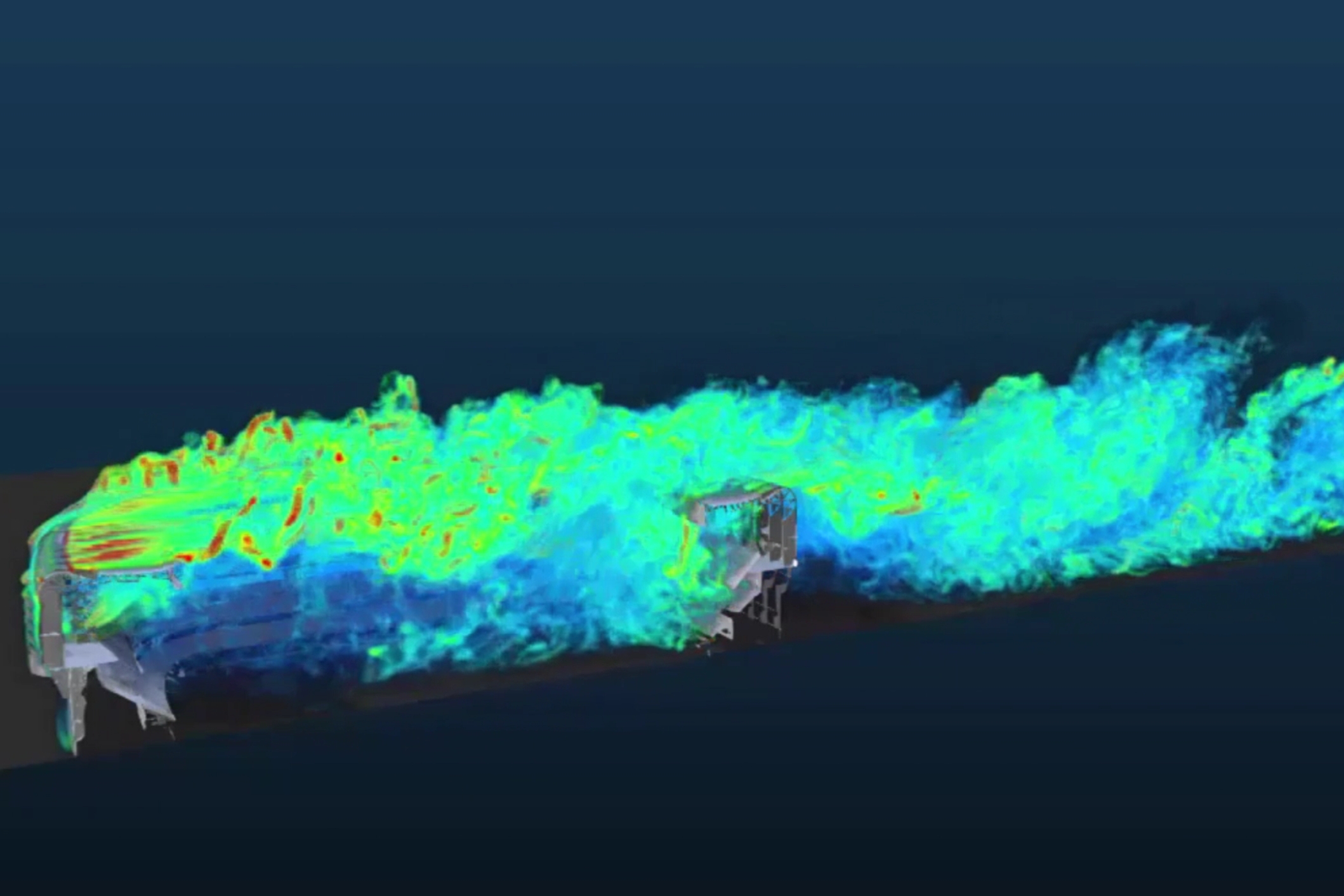

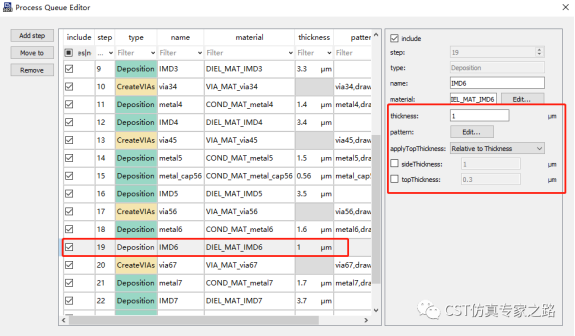

再来看对sidethickness和topthickness都没指定设置的情况,只设了thickness为1。

从下图可以看出,正如前文所说,sidethickness和topthickness均为1um,在金属线的周围是一个均匀厚度的1um共形。

搞清楚共形如何设置之后,我们就可以根据实际需要进行共形设置了。

(内容、图片来源:cst仿真专家之路公众号,侵删)

博天堂登陆的版权与免责声明:

凡未注明作者、来源的内容均为转载稿,如出现博天堂登陆的版权问题,请及时联系918博天堂官网处理。我们对页面中展示内容的真实性、准确性和合法性均不承担任何法律责任。如内容信息对您产生影响,请及时联系918博天堂官网修改或删除。

-

2023-12-29

-

2023-12-29

-

2023-12-29

-

2023-12-28

-

2023-12-28

-

2023-12-28

-

2023-12-27

-

2023-12-27

-

2023-12-27

-

2023-12-26

-

[abaqus] abaqus如何建模?abaqus有限元......

2023-07-07

-

2023-08-24

-

[abaqus] 关于2013版的thinkdesign用......

2014-06-20

-

2017-05-19

-

[abaqus] thinkdesign技术在创新设计中的......

2015-03-03

-

[abaqus] 基于thinkdesign回弹补偿功能的......

2015-03-03

-

[abaqus] td styling之眼镜三维建模、渲染......

2015-03-03

-

2015-03-03

-

2023-08-29

-

2015-03-03

-

[有限元知识] abaqus分析指南120:裂纹萌生与扩......

2023-12-29

-

[有限元知识] abaqus分析指南119:将内聚材料概......

2023-12-29

-

2023-12-29

-

2023-12-28

-

[有限元知识] abaqus分析指南116:多个丰富的功......

2023-12-28

-

[有限元知识] abaqus分析指南115:用水平集方法......

2023-12-27

-

[有限元知识] abaqus分析指南114:水力驱动裂缝......

2023-12-27

-

[有限元知识] abaqus分析指南113:基于内聚段法......

2023-12-26

-

[有限元知识] abaqus分析指南112:有限元方法将......

2023-12-26

-

[有限元知识] abaqus分析指南111:温度和场变量......

2023-12-26

地址: 广州市天河区天河北路663号广东省机械研究所8栋9层 电话:020-38921052 传真:020-38921345 邮箱:thinks@think-s.com

博天堂登陆 copyright © 2010-2023 广州思茂信息科技有限公司 all rights reserved. 粤icp备11003060号-2